# **TA100 Automotive**

# **TA100** CryptoAutomotive<sup>™</sup> Security IC

## **Description**

The Microchip Technology Inc. Trust Anchor security device TA100 is intended for automotive, industrial, or commercial systems and can provide support for code authentication (secure boot), Message Authentication Code (MAC) generation, support for trusted firmware updates, multiple key management protocols including Transport Layer Security (TLS), and other root-of-trust-based operations.

It is typically a companion device to an MCU or MPU on the same board.

## **Features**

- · Advanced Crypto Engine (ACE) for Execution of All Cryptography Commands

- · Fast Crypto Engine for SHA-256, HMAC, and AES-CMAC Algorithms

- ECDSA Sign/Verify Support:

- P224, P256, P384, and 256-bit Brainpool elliptic curves

- SECP256K1 (Bitcoin/Blockchain) curve

- ECDH/ECDHE/ECBD Key Agreement Support

- Elliptic-Curve Diffie-Hellman (ECDH) Support for P224, P256, and 256-bit Brainpool

- Elliptic-Curve Burmeiseter-Desmedt (ECBD) Support for P224 Curve

- Internal Symmetric and Asymmetric Key Generation and Derivation:

- P224, P256, P384 and 256-Bit Brainpool

- 2048-bit RSA keys

- AES 16-byte keys

- · AES and RSA Encryption / Decryption Support

- AES ECB/GCM Encryption/Decryption Supported directly

- RSA 1024-bit and 2048-bit Keys Encryption/Decryption Support

- NIST SP800-90 Random Number Generator (RNG)

- Multiple I/O Options for Security Commands Include:

- 1 MHz standard I<sup>2</sup>C interface

- 16 MHz SPI interface

- · Package Options:

- 8-lead SOIC

- 14-lead SOIC

- 24-pad 4 x 4 mm VQFN (Contact Microchip Sales to determine the availability of this packaging option.)

- Voltage Supply Range: 2.7V to 5.5V

- Automotive Temperature Range: -40°C to +125°C Ambient Operating Range

# **Applications**

- Full and Partial Secure Boot

- Secure Firmware Update

- CAN Message Authentication

- WPC 1.3 Qi High Power Transmitter Authentication

- High-Bandwidth Digital Content Protection (HDCP) Cryptographic Support

- Network Authentication and Session Establishment using TLS

- · Electric Vehicle (EV) Battery Authentication

# **Table of Contents**

| De  | escription                                                  | 1  |

|-----|-------------------------------------------------------------|----|

| Fe  | atures                                                      | 1  |

| Ар  | plications                                                  | 1  |

| 1.  | Pin Configuration                                           | 4  |

|     | 1.1. SOIC-8 Pinout with SPI Interface                       |    |

|     | 1.2. SOIC-8 Pinout with I <sup>2</sup> C Interface          | 4  |

|     | 1.3. SOIC-14 Pinout with I <sup>2</sup> C and SPI Interface | 5  |

|     | 1.4. VQFN-24 Pinout with I <sup>2</sup> C and SPI Interface | 6  |

| 2.  | Overview                                                    | 8  |

| 3.  | Device Features                                             | 9  |

| 4.  | Nonvolatile Memory                                          | 10 |

| 5.  | Security Features                                           | 11 |

| 6.  | Electrical Characteristics                                  | 12 |

|     | 6.1. Absolute Maximum Ratings                               | 12 |

|     | 6.2. DC Characteristics                                     | 12 |

|     | 6.3. AC Characteristics                                     | 13 |

| 7.  | Package Marking Information                                 | 17 |

| 8.  | Package Drawings                                            | 18 |

|     | 8.1. 8-Lead SOIC                                            | 18 |

|     | 8.2. 14-Lead SOIC                                           | 21 |

|     | 8.3. 24-Pad VQFN                                            | 24 |

| 9.  | Revision History                                            | 27 |

| Th  | e Microchip Website                                         | 28 |

| Pro | oduct Change Notification Service                           | 28 |

| Cu  | istomer Support                                             | 28 |

| Pro | oduct Identification System                                 | 29 |

| Mic | crochip Devices Code Protection Feature                     | 30 |

| Le  | gal Notice                                                  | 30 |

| Tra | ademarks                                                    | 31 |

| Qu  | uality Management System                                    | 31 |

| Wc  | orldwide Sales and Service                                  | 32 |

# 1. Pin Configuration

The TA100 device comes in four package configuration options based on the desired I/O interface. These include:

- · SPI only interface in 8-pin SOIC

- I<sup>2</sup>C only interface in 8-pin SOIC

- SPI and I<sup>2</sup>C interfaces in 14-pin SOIC

- SPI and I<sup>2</sup>C interfaces in 24-pad VQFN

Based on the configuration selected, different GPIO options are available.

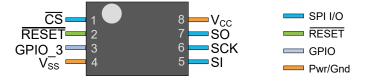

## 1.1 SOIC-8 Pinout with SPI Interface

The 8-pin SOIC SPI interface consists of the four SPI signals, a Reset signal and GPIO 3.

Table 1-1. 8-Pin SOIC SPI Pin Configuration

| Pin Name        | Pin Number | Function                |

|-----------------|------------|-------------------------|

| CS              | 1          | Chip Select for SPI     |

| RESET           | 2          | Reset Input, active low |

| GPIO_3          | 3          | GPIO_3                  |

| V <sub>SS</sub> | 4          | Ground                  |

| SI              | 5          | SPI Serial Data Input   |

| SCK             | 6          | SPI Clock               |

| so              | 7          | SPI Serial Data Output  |

| V <sub>CC</sub> | 8          | 2.7V-5.5V Power Supply  |

Figure 1-1. Pinout

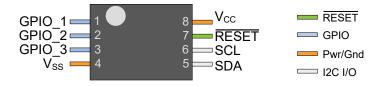

## 1.2 SOIC-8 Pinout with I<sup>2</sup>C Interface

Pull-up resistors are required for proper operation of the  $I^2C$  bus, sized according to the board configuration and bus speed per the  $I^2C$  specification.

Table 1-2. 8-Pin SOIC I<sup>2</sup>C Pin Configuration

| Pin Name | Pin Number | Function |

|----------|------------|----------|

| GPIO_1   | 1          | GPIO_1   |

| GPIO_2   | 2          | GPIO_2   |

| GPIO_3   | 3          | GPIO_3   |

| continued       |            |                         |  |  |  |  |

|-----------------|------------|-------------------------|--|--|--|--|

| Pin Name        | Pin Number | Function                |  |  |  |  |

| V <sub>SS</sub> | 4          | Ground                  |  |  |  |  |

| SDA             | 5          | I <sup>2</sup> C Data   |  |  |  |  |

| SCL             | 6          | I <sup>2</sup> C Clock  |  |  |  |  |

| RESET           | 7          | Reset Input, active low |  |  |  |  |

| V <sub>CC</sub> | 8          | 2.7V-5.5V Power Supply  |  |  |  |  |

Figure 1-2. Pinout

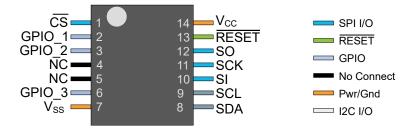

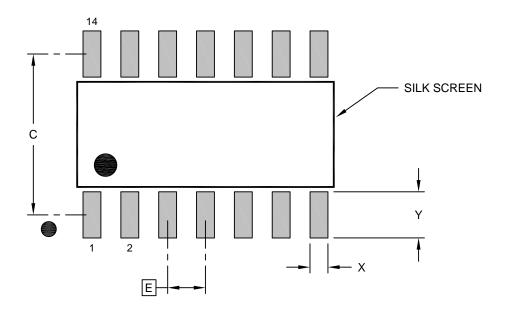

## 1.3 SOIC-14 Pinout with I<sup>2</sup>C and SPI Interface

In the 14-pin package, there is access to both the  $I^2C$  and SPI bus pins. Both can be used simultaneously. However, any concurrent transactions must be to different blocks in the device.

Pull-up resistors are required for proper operation of the  $I^2C$  bus, sized according to the board configuration and bus speed required per the  $I^2C$  specification.

Table 1-3. 14-Pin SOIC Pin Configuration

| Pin Name        | Pin Number | Function                 |

|-----------------|------------|--------------------------|

| CS              | 1          | Chip Select for SPI      |

| GPIO_1          | 2          | General Purpose I/O pin  |

| GPIO_2          | 3          | General Purpose I/O pin  |

| NC              | 4, 5       | Not Internally Connected |

| GPIO_3          | 6          | General Purpose I/O pin  |

| V <sub>SS</sub> | 7          | Ground                   |

| SDA             | 8          | I <sup>2</sup> C Data    |

| SCL             | 9          | I <sup>2</sup> C Clock   |

| SI              | 10         | SPI Serial Data Input    |

| SCK             | 11         | SPI Clock                |

| so              | 12         | SPI Serial Data Output   |

| RESET           | 13         | Reset Input, active low  |

| V <sub>CC</sub> | 14         | 2.7V-5.5V Power Supply   |

Figure 1-3. Pinout

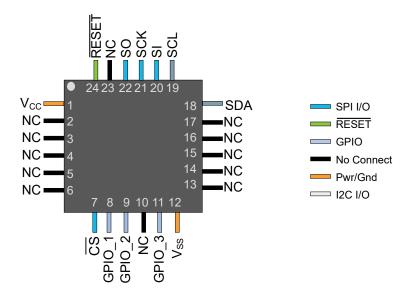

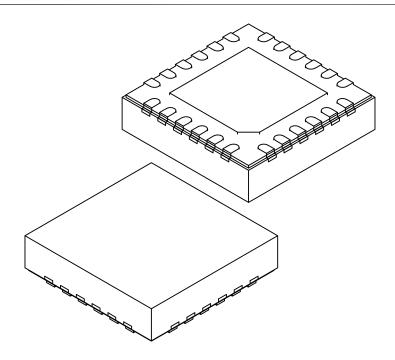

## 1.4 VQFN-24 Pinout with I<sup>2</sup>C and SPI Interface

In the 24-pin VQFN package, there is access to both the  $I^2C$  and SPI bus pins. Both can be used simultaneously. However, any concurrent transactions must be to different blocks in the device.

Pull-up resistors are required for proper operation of the  $I^2C$  bus, sized according to the board configuration and bus speed required per the  $I^2C$  specification.

Table 1-4. 24-Pin VQFN Pin Configuration

| Pin Name        | Pin Number                                      | Function                 |

|-----------------|-------------------------------------------------|--------------------------|

| V <sub>CC</sub> | 1                                               | 2.7V-5.5V Power Supply   |

| NC              | 2, 3, 4, 5, 6, 10,<br>13, 14, 15, 16,<br>17, 23 | Not Internally Connected |

| CS              | 7                                               | Chip Select for SPI      |

| GPIO_1          | 8                                               | General Purpose I/O pin  |

| GPIO_2          | 9                                               | General Purpose I/O pin  |

| GPIO_3          | 11                                              | General Purpose I/O pin  |

| V <sub>SS</sub> | 12                                              | Ground                   |

| SDA             | 18                                              | I <sup>2</sup> C Data    |

| SCL             | 19                                              | I <sup>2</sup> C Clock   |

| SI              | 20                                              | SPI Serial Data Input    |

| SCK             | 21                                              | SPI Clock                |

| so              | 22                                              | SPI Serial Data Output   |

| RESET           | 24                                              | Reset Input, active low  |

Note: The exposed paddle is electrically isolated from the die. It is recommended that this be connected to GND.

Figure 1-4. Pinout

## 2. Overview

The TA100 security device interfaces with a host MCU to provide a hardened root of trust with symmetric and asymmetric computation ability to facilitate a number of security related capabilities within an automotive system:

- · Secure boot support:

- Host code image and signature validation

- Secure encryption key storage and image encryption

- Authenticated update of the code validation public key

- X.509 certificate storage, parsing, validation, and revocation, supporting both ECC and RSA

- · Fully internal random key generation for RSA, ECC, and AES

- · Monotonic counters protected against tearing

- · Elliptic curves support:

- P224 ECDSA sign, verify, ECDH, and ECBD

- P256 ECDSA sign, verify, and ECDH

- SECP256K1 (Bitcoin/Blockchain) ECDSA support

- 256-bit Brainpool ECDSA and ECDH

- P384 ECDSA sign and verify

- · RSA support:

- 1024-bit and 2048-bit RSA OAEP/MGF encrypt/decrypt

- 2048-bit RSA signature generation and verification

- 3072-bit RSA verification

- ECDH key management capability with integrated KDF, either PRF or HKDF

- NIST SP800-90 A/B/C high-quality cryptographic random number generation

- TLS V1.2/V1.3 full session establishment support in conjunction with host SW

- AES-CMAC calculation and validation

- AES-ECB and GCM encrypt/decrypt for general purpose use

- SHA-256 and SHA-HMAC digest calculation

- · Input/output encryption and authentication using AES-GCM, AES-CMAC, and/or SHA-HMAC

- · Flexible self-test support to meet FIPS 140 requirements

- Cryptographic support for High-Bandwidth Digital Content Protection (HDCP) V2.2

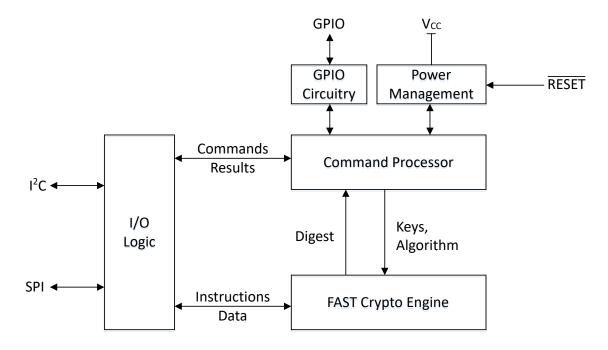

The TA100 device contains two processing blocks:

- 1. A main command processor that implements an Advanced Crypto Engine along with the management and session establishment functionality. The ACE can implement all symmetric and asymmetric crypto functions.

- 2. A Fast Crypto Engine capable of implementing AES and SHA calculations in parallel with the operation of the main command processor.

## 3. Device Features

The TA100 device supports several broad features, including secure boot (host code authentication), MAC generation, secure key, and certificate storage and management.

Public information stored within the protected memory, such as code digests, certificate validation status, public keys, etc., can only be modified when properly authorized by using the specified protocols in this data sheet.

The TA100 is powered by an internal microcontroller running dedicated software loaded into the ROM and nonvolatile memory during chip manufacture. Nonvolatile memory is used for certificate storage and secret/private key storage. There is no direct access to the memories from the external pins of the device and there is no available programming or debug interface.

The block diagram of the TA100 shows the major architectural features of the device.

Figure 3-1. TA100 Block Diagram

# 4. Nonvolatile Memory

The nonvolatile memory within the TA100 device is split into three pieces:

**Configuration** In general, this area is expected to be written prior to the placement of the TA100 device on the application board. Once the configuration is complete, this area must be locked to prevent

further modification and for proper device operation.

**Shared Data**This area can be used for keys, secrets, certificates, and/or data. The TA100 does not place **Memory:**any requirements on the arrangement or distribution of items stored within this block other

than the overall limit on the space available to all the shared elements.

**Dedicated Data** Certain other items are stored within the device and are managed directly by various

Memory: commands.

# 5. Security Features

The TA100 device includes protection against both active (invasive) and passive (noninvasive) attacks on the certificates, private and symmetric keys stored within the device. Specific hardware and firmware elements are included to prevent environmental (voltage, temperature, and frequency) attacks, emissions attacks, fault attacks, physical attacks, cloning, and many other attack methodologies. All internal memory for private/symmetric keys or other secret data is encrypted.

## 6. Electrical Characteristics

## 6.1 Absolute Maximum Ratings

Ambient Temperature under Bias<sup>(1)</sup>

Storage Temperature (without Bias)

-65°C to +150°C

Maximum Supply Voltage

6.0V

DC Voltage on Any Pin<sup>(4)</sup>

ESD Ratings

— Human Body Model (HBM) ESD<sup>(2)</sup>

— Charged Device Model (CDM) ESD<sup>(3)</sup>

-40°C to +125°C

6.0V

-0.5 to  $V_{CC}$  + 0.5  $= \pm 4 \text{ kV}$   $= \pm 750 \text{ V}$

#### Notes:

- Recent Partial Networking Transceivers from Microchip and others use a spec throughout the document called the Virtual Junction Temperature, measured in accordance with IEC60747-1. An alternate definition is T<sub>VJ</sub> = T<sub>A</sub> + P x R<sub>th(j-a)</sub>, where P is the power and R<sub>th(j-a)</sub> is the thermal resistance from virtual junction to ambient. T<sub>VJ</sub> would be higher than +125°C (maximum).

- 2. Specified by: Jedec Standard JS-001-2017

- 3. Specified by: Jedec Standard JS-002-2014

- V<sub>CC</sub> is the supply voltage to which the device is driven and must be within the specified operating voltage range.

**Note:** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### 6.2 DC Characteristics

#### Table 6-1. DC Characteristics - All Interfaces

Applicable over the recommended operating range from  $T_A$  = -40°C to +125°C,  $V_{CC}$  = +2.7V to +5.5V.

| Parameters                            | Test Conditions                                   | Symbol                 | Min.                  | Тур. | Max.                  | Units | Туре |

|---------------------------------------|---------------------------------------------------|------------------------|-----------------------|------|-----------------------|-------|------|

| Supply Voltage on Pin V <sub>CC</sub> |                                                   | V <sub>CC</sub>        | 2.7                   | _    | 5.5                   | V     | Α    |

| Supply Current on Pin V <sub>CC</sub> | Active mode <sup>(4)</sup>                        | I <sub>IO_Active</sub> | _                     | 25   | 40                    | mA    | Α    |

|                                       | Idle mode <sup>(2)</sup> (T <sub>A</sub> = +85°C) | I <sub>IO_Idle</sub>   | _                     | _    | 10                    | mA    | В    |

|                                       | Sleep mode                                        | I <sub>IO_Sleep</sub>  | _                     | 7    | 15                    | uA    | В    |

| V <sub>CC</sub> Rise Rate             |                                                   | V <sub>RISE</sub>      | _                     | _    | 0.1                   | V/µs  | С    |

| High-Level Input Voltage              |                                                   | V <sub>IH</sub>        | 0.7 x V <sub>CC</sub> | _    | V <sub>CC</sub> + 0.3 | V     | Α    |

| Low-Level Input Voltage               |                                                   | V <sub>IL</sub>        | -0.3                  | _    | 0.3 x V <sub>CC</sub> | V     | Α    |

- 1. Type means: A = 100% tested, B = characterized, C = design parameter.

- 2. Idle means that power is applied, the device is NOT in Sleep mode and no commands nor instructions are running.

- 3. The state of the V<sub>CC</sub> latches will be retained so long as V<sub>CC</sub> remains above the V<sub>POR</sub> level.

- 4. Active current is measured with all GPIO pins either driven to ground or configured as inputs. Active current also excludes any DC load on the I/O pins.

Table 6-2. DC Characteristics – SPI Interface, RESET and GPIO Pins

Applicable over the recommended operating range from  $T_A = -40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$ ,  $V_{CC} = +2.7V$  to +5.5V.

| Parameters                   | Test Conditions                              | Symbol          | Min.                  | Тур. | Max. | Units | Туре |

|------------------------------|----------------------------------------------|-----------------|-----------------------|------|------|-------|------|

| Input Current <sup>(1)</sup> | 0.1V <sub>CC</sub> < Vi < 0.9V <sub>CC</sub> | Ι <sub>L</sub>  | -2                    | _    | +2   | μΑ    | Α    |

| Programmable Pull-Up         |                                              | R <sub>PU</sub> | 24K                   | 40K  | 56K  | Ω     | Α    |

| High-Level Output Voltage    | I <sub>OH</sub> = -4 mA                      | V <sub>OH</sub> | V <sub>CC</sub> – 0.4 | _    | _    | V     | Α    |

| Low-Level Output Voltage     | I <sub>OL</sub> = 4 mA                       | V <sub>OL</sub> | _                     | _    | 0.4  | V     | Α    |

#### Note:

1. This specification is only valid when the internal pull-ups are disabled. Otherwise, the input current is determined by the internal pull-up resistance value R<sub>PU</sub>.

### Table 6-3. DC Characteristics of SDA and SCL Pins for I<sup>2</sup>C Interface

Applicable over the recommended operating range from  $T_A = -40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$ ,  $V_{CC} = +2.7V$  to +5.5V.

| Parameters                   | Test Conditions                                           | Symbol          | Min. | Тур  | Max. | Units | Type <sup>(1)</sup> |

|------------------------------|-----------------------------------------------------------|-----------------|------|------|------|-------|---------------------|

| Input Current <sup>(2)</sup> | 0.1V <sub>CC</sub> < Vi < 0.9V <sub>CC</sub>              | li              | -10  | _    | +10  | μΑ    | Α                   |

| Low-Level Output Voltage     | $I_{OL}$ = 20 mA<br>$V_{CC}$ > 3.6V to 5.5V               | V <sub>OL</sub> | 0    | _    | 0.4  | V     | В                   |

|                              | I <sub>OL</sub> = 14 mA<br>V <sub>CC</sub> = 2.7V to 3.6V | V <sub>OL</sub> | 0    | _    | 0.4  | V     | В                   |

| Programmable Pull-Up         |                                                           | R <sub>PU</sub> | 2.3K | 3.0K | 4.5K | Ω     | Α                   |

#### Notes:

- 1. Type means: A = 100% tested, B = characterized on samples, C = design parameter.

- The input current specification is only valid when the internal pull-ups are disabled. Otherwise, the input current is determined by the internal pull-up resistance value R<sub>PU</sub>.

#### 6.3 AC Characteristics

#### 6.3.1 All Interfaces

#### Table 6-4. AC Timing Characteristics - All Interfaces

Applicable over the recommended operating range from  $T_A = -40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$ ,  $V_{CC} = +2.7V$  to +5.5V.

| Symbol                              | Parameters                                            | Min. | Тур. | Max. | Units |

|-------------------------------------|-------------------------------------------------------|------|------|------|-------|

| t <sub>PU.SLEEP</sub> (1)           | Wake-up time from Sleep state. V <sub>CC</sub> > 2.7V | _    | 3    | 5    | ms    |

| t <sub>PU.POWERON</sub> (1)         | Power-up time from $V_{CC}$ < 2.7V                    | _    | 4    | 6    | ms    |

| t <sub>IDLE</sub> <sup>(2, 4)</sup> | Idle timer                                            | 0.85 | 1    | 1.15 | S     |

| continue                             | continued                                                                       |      |      |       |       |  |  |  |  |  |

|--------------------------------------|---------------------------------------------------------------------------------|------|------|-------|-------|--|--|--|--|--|

| Symbol                               | Parameters                                                                      | Min. | Тур. | Max.  | Units |  |  |  |  |  |

| t <sub>MONOTONIC</sub> (4)           | Rate at which the nonvolatile portion of monotonic counter increments           | 42   | 51   | 60    | S     |  |  |  |  |  |

| t <sub>RESET_NOISE</sub> (3)         | Noise suppression on RESET input pin                                            | 0    | _    | 0.150 | μs    |  |  |  |  |  |

| t <sub>RESET_MIN</sub> (3)           | Minimum allowed reset pulse                                                     | 1.0  | _    | _     | μs    |  |  |  |  |  |

| t <sub>SLEEP_WAKE</sub>              | GPIO_3 transition ignored, measured starting with the last bit of Power (Sleep) | _    | _    | 250   | μs    |  |  |  |  |  |

| t <sub>WAKE_GPIO_LOW</sub>           | Low-pulse width for GPIO_3 high to wake TA100                                   | 40   | _    | _     | μs    |  |  |  |  |  |

| t <sub>WATCHDOG</sub> <sup>(4)</sup> | Watchdog timeout value.                                                         | 900  | 1000 | 1100  | ms    |  |  |  |  |  |

- 1. Various situations can cause the power-up delays to exceed these parameters as follows:

- If the power-on or the wake self-test functions are enabled in the configuration area, the execution of those self-test operations will increase the delay.

- If an internal failure occurs to cause a boot event, then, there may be additional delay during the boot to write the internal failure log in the nonvolatile memory within the chip.

- If a device update is started but does not complete due to a power interruption, on the next power-up, some cleanup may be required and may take additional time.

- If the 1 minute timer is enabled and is being updated in the nonvolatile memory concurrent with the wake event, the device will accept an Input command after t<sub>PU\_SLEEP</sub>/t<sub>PU\_POWERON</sub>, but will not start the execution of that command until the nonvolatile update is complete.

- The idle timer specifications here assume that the idle timer is enabled and configured for 1 second. It is recommended that these times be multiplied by the delay time value set in the idle timer configuration field if that is not 1.

- All noise pulses ≤ t<sub>RESET\_NOISE</sub> are assured to be suppressed. All pulse widths ≥ t<sub>RESET\_MIN</sub> are assured to pass to the device. Pulses in between these values may or may not be suppressed.

- 4. This specification is characterized but not production tested.

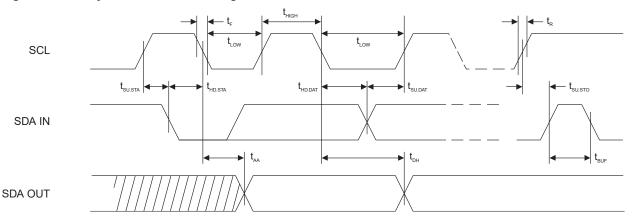

### 6.3.2 I<sup>2</sup>C Interface Timing

## Table 6-5. AC Characteristics of I<sup>2</sup>C Interface

Applicable over the recommended operating range from  $T_A = -40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$ ,  $V_{CC} = +2.7V$  to +5.5V.

| Symbol              | Parameters                        | Fast-Mode Plus                              |      | Units |

|---------------------|-----------------------------------|---------------------------------------------|------|-------|

|                     |                                   | Min.                                        | Max. |       |

| f <sub>SCL</sub>    | SCL Clock Frequency               | _                                           | 1000 | kHz   |

| t <sub>HIGH</sub>   | SCL High Time                     | 260                                         | _    | ns    |

| t <sub>LOW</sub>    | SCL Low Time                      | 500                                         | _    | ns    |

| t <sub>SU.STA</sub> | Start Setup Time                  | 260                                         | _    | ns    |

| t <sub>HD.STA</sub> | Start Hold Time                   | 260                                         | _    | ns    |

| t <sub>SU.STO</sub> | Stop Setup Time                   | 260                                         | _    | ns    |

| t <sub>SU.DAT</sub> | Data in Setup Time                | 50                                          | _    | ns    |

| t <sub>HD.DAT</sub> | Data in Hold Time                 | 0                                           | _    | ns    |

| t <sub>R</sub>      | Input Rise Time <sup>(1, 3)</sup> | _                                           | 120  | ns    |

| t <sub>F</sub>      | Input Fall Time <sup>(1, 3)</sup> | 20 x (V <sub>DD</sub> /5.5V) <sup>(5)</sup> | 120  | ns    |

| t <sub>AA</sub>     | Clock Low to Data Out Valid       | _                                           | 450  | ns    |

| continued        |                                                                                  |               |      |       |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------|---------------|------|-------|--|--|--|--|--|

| Symbol           | Parameters                                                                       | Fast-Mode Plu | ıs   | Units |  |  |  |  |  |

|                  |                                                                                  | Min.          | Max. |       |  |  |  |  |  |

| t <sub>BUF</sub> | Time bus must be free before a new transmission can start. (1)                   | 500           | _    | ns    |  |  |  |  |  |

| t <sub>SP</sub>  | Pulse width of spikes that must be suppressed by the input filter <sup>(4)</sup> | _             | 50   | ns    |  |  |  |  |  |

- 1. Values are based on characterization and are not tested.

- 2. AC measurement conditions: input pulse voltages:  $0.3 \times V_{CC}$  to  $0.7 \times V_{CC}$ , input rise and fall times:  $\leq 50 \text{ ns.}$

- System designers must ensure that all AC parametrics are met. Rise fall times shown are for the Fast Mode Plus (1 MHz) of operation. For slower clock speeds, the rise and fall times may be increased but must still meet the industry standard I<sup>2</sup>C specification UM10204.

- 4. Input filters on the SDA and SCL pins will suppress noise spikes of less than 50 ns.

- 5. Backwards compatibility is necessary for the Fast mode (400 kHz) specifications.

Figure 6-1. I<sup>2</sup>C Synchronous Data Timing

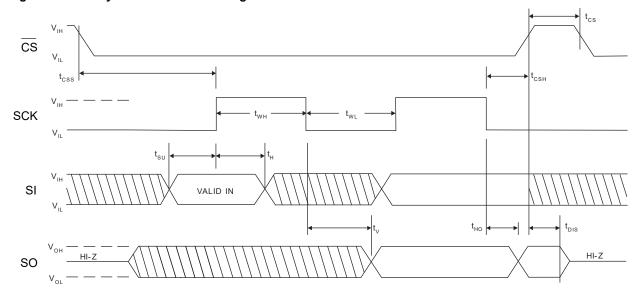

#### 6.3.3 SPI Interface Timing

#### Table 6-6. AC Characteristics of SPI Interface

Applicable over the recommended operating range from  $T_A = -40$ °C to +125°C,  $V_{CC} = +2.7$ V to +5.5V.

| Symbol           | Parameters                        | Min. | Max. | Units |

|------------------|-----------------------------------|------|------|-------|

| f <sub>SCK</sub> | SCK Clock Frequency               | _    | 16   | MHz   |

| t <sub>WH</sub>  | SCK High Time                     | 20   | _    | ns    |

| t <sub>WL</sub>  | SCK Low Time                      | 25   | _    | ns    |

| t <sub>CS</sub>  | CS High Time                      | 100  | _    | ns    |

| t <sub>CSS</sub> | CS Setup Time                     | 100  | _    | ns    |

| t <sub>CSH</sub> | CS Hold Time                      | 100  | _    | ns    |

| t <sub>SU</sub>  | Data in Setup Time                | 5    | _    | ns    |

| t <sub>H</sub>   | Data in Hold Time                 | 5    | _    | ns    |

| t <sub>RI</sub>  | Input Rise Time <sup>(1, 2)</sup> | _    | 2    | μs    |

| t <sub>FI</sub>  | Input Fall Time <sup>(1, 2)</sup> |      | 2    | μs    |

| t <sub>V</sub>   | Output Valid                      | _    | 25   | ns    |

| continued        |                     |      |      |       |  |  |  |

|------------------|---------------------|------|------|-------|--|--|--|

| Symbol           | Parameters          | Min. | Max. | Units |  |  |  |

| t <sub>HO</sub>  | Output Hold Time    | 0    | _    | ns    |  |  |  |

| t <sub>DIS</sub> | Output Disable Time | _    | 25   | ns    |  |  |  |

- 1. Values are based on characterization and are not production tested.

- 2. System designers must ensure that all AC parametrics are met, which will typically require rise and fall times faster than these values for most clock rates. Ramp rates slower than this may result in improper operation.

Figure 6-2. SPI Synchronous Data Timing

## **TA100 Automotive**

## **Package Marking Information**

# 7. Package Marking Information

As part of Microchip's overall security features, the part marking for all crypto devices is intentionally vague. The marking on the top of the package does not provide any information as to the actual device type or the manufacturer of the device. The alphanumeric code on the package provides manufacturing information and will vary with assembly lot. It is recommended that the packaging mark not be used as part of any incoming inspection procedure to identify the device.

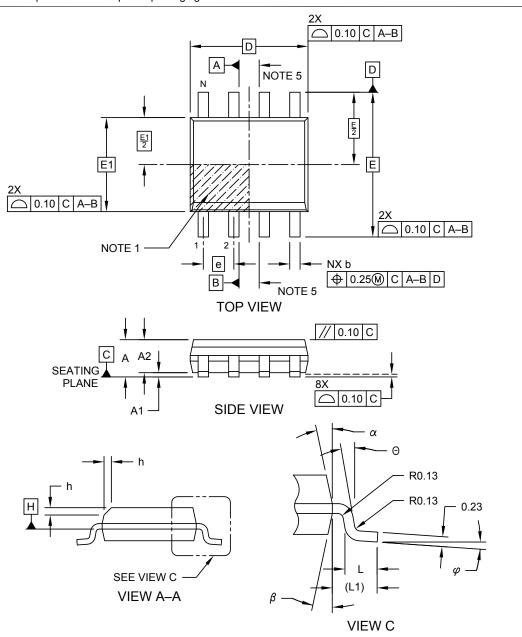

# 8. Package Drawings

## 8.1 8-Lead SOIC

## 8-Lead Plastic Small Outline (OA) - Narrow, 3.90 mm (.150 ln.) Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing No. C04-057-OA Rev F Sheet 1 of 2

## 8-Lead Plastic Small Outline (OA) - Narrow, 3.90 mm (.150 ln.) Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |          |          |      |  |

|--------------------------|-------------|----------|----------|------|--|

| Dimension                | MIN         | NOM      | MAX      |      |  |

| Number of Pins           | Ν           |          | 8        |      |  |

| Pitch                    | е           |          | 1.27 BSC |      |  |

| Overall Height           | Α           | 1        | ı        | 1.75 |  |

| Molded Package Thickness | A2          | 1.25     | ı        | -    |  |

| Standoff §               | A1          | 0.10     | -        | 0.25 |  |

| Overall Width            | Е           | 6.00 BSC |          |      |  |

| Molded Package Width     | E1          | 3.90 BSC |          |      |  |

| Overall Length           | D           |          | 4.90 BSC |      |  |

| Chamfer (Optional)       | h           | 0.25     | -        | 0.50 |  |

| Foot Length              | L           | 0.40     | -        | 1.27 |  |

| Footprint                | L1          | 1.04 REF |          |      |  |

| Foot Angle               | φ           | 0°       | ı        | 8°   |  |

| Lead Thickness           | С           | 0.17     | -        | 0.25 |  |

| Lead Width               | b           | 0.31     | -        | 0.51 |  |

| Mold Draft Angle Top     | α           | 5°       | -        | 15°  |  |

| Mold Draft Angle Bottom  | β           | 5°       | -        | 15°  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M  $\,$

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing No. C04-057-OA Rev F Sheet 2 of 2

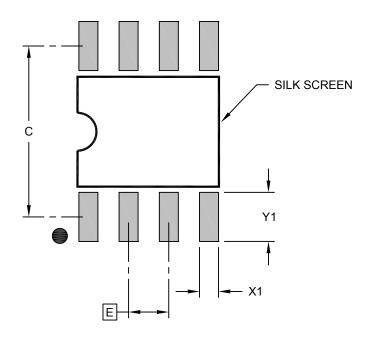

## 8-Lead Plastic Small Outline (OA) - Narrow, 3.90 mm (.150 ln.) Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### RECOMMENDED LAND PATTERN

|                         | MILLIMETERS |          |      |      |

|-------------------------|-------------|----------|------|------|

| Dimension               | MIN         | NOM      | MAX  |      |

| Contact Pitch           | Е           | 1.27 BSC |      |      |

| Contact Pad Spacing     | С           |          | 5.40 |      |

| Contact Pad Width (X8)  | X1          |          |      | 0.60 |

| Contact Pad Length (X8) | Y1          |          |      | 1.55 |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-2057-OA Rev F

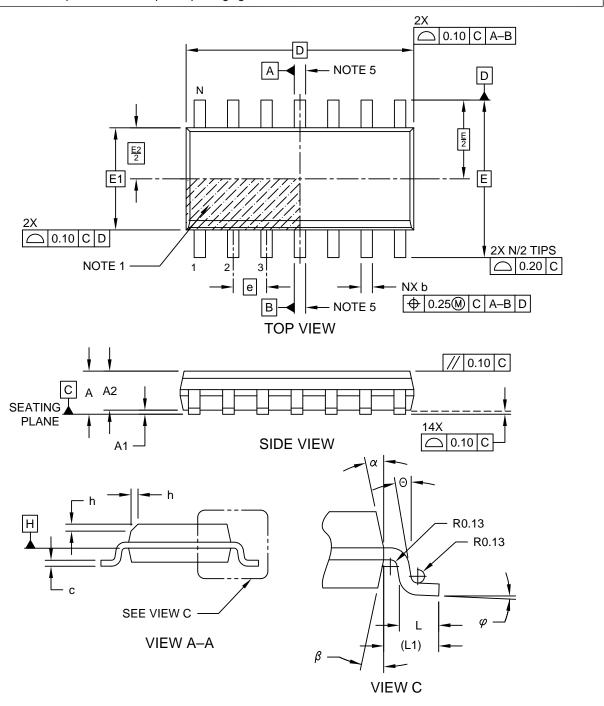

## 8.2 14-Lead SOIC

# 14-Lead Plastic Small Outline (D3X, UEB, M5B, UEB) - Narrow, 3.90 mm Body [SOIC] Atmel Legacy Global Package Code SVQ

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing No. C04-065-D3X Rev D

# 14-Lead Plastic Small Outline (D3X, UEB, M5B, UEB) - Narrow, 3.90 mm Body [SOIC] Atmel Legacy Global Package Code SVQ

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |          |          |      |  |

|--------------------------|-------------|----------|----------|------|--|

| Dimension                | MIN         | NOM      | MAX      |      |  |

| Number of Pins           | N           |          | 14       |      |  |

| Pitch                    | е           |          | 1.27 BSC |      |  |

| Overall Height           | Α           | ı        | -        | 1.75 |  |

| Molded Package Thickness | A2          | 1.25     | -        | -    |  |

| Standoff §               | A1          | 0.10     | -        | 0.25 |  |

| Overall Width            | Е           |          | 6.00 BSC |      |  |

| Molded Package Width     | E1          | 3.90 BSC |          |      |  |

| Overall Length           | D           | 8.65 BSC |          |      |  |

| Chamfer (Optional)       | h           | 0.25     | -        | 0.50 |  |

| Foot Length              | L           | 0.40     | -        | 1.27 |  |

| Footprint                | L1          |          | 1.04 REF |      |  |

| Lead Angle               | Θ           | 0°       | -        | -    |  |

| Foot Angle               |             | 0°       | -        | 8°   |  |

| Lead Thickness           | С           | 0.10     | -        | 0.25 |  |

| Lead Width               | b           | 0.31     | -        | 0.51 |  |

| Mold Draft Angle Top     | α           | 5°       | -        | 15°  |  |

| Mold Draft Angle Bottom  | β           | 5°       | -        | 15°  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic

- Dimension D does not include mold flash, protrusions or gate burrs, which shall not exceed 0.15 mm per end. Dimension E1 does not include interlead flash or protrusion, which shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

- 5. Datums A & B to be determined at Datum H.

Microchip Technology Drawing No. C04-065-D3X Rev D Sheet 2 of 2

# 14-Lead Plastic Small Outline (D3X, UEB, M5B, UEB) - Narrow, 3.90 mm Body [SOIC] Atmel Legacy Global Package Code SVQ

e: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                          | MILLIMETERS |     |          |      |

|--------------------------|-------------|-----|----------|------|

| Dimension                | MIN         | NOM | MAX      |      |

| Contact Pitch            | Е           |     | 1.27 BSC |      |

| Contact Pad Spacing      | С           |     | 5.40     |      |

| Contact Pad Width (X14)  | Х           |     |          | 0.60 |

| Contact Pad Length (X14) | Υ           |     |          | 1.55 |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2065-D3X Rev D

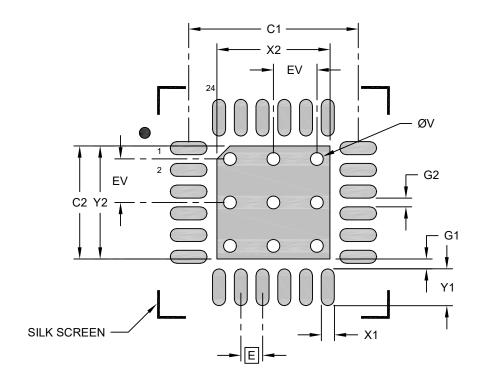

## 8.3 24-Pad VQFN

# 24-Lead Very Thin Plastic Quad Flat, No Lead Package (UFB) - 4x4x1.0 mm Body [VQFN] With 2.50 mm Exposed Pad and Stepped Wettable Flanks

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-21549 Rev A Sheet 1 of 2

## 24-Lead Very Thin Plastic Quad Flat, No Lead Package (UFB) - 4x4x1.0 mm Body [VQFN] With 2.50 mm Exposed Pad and Stepped Wettable Flanks

For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                                | MILLIMETERS |           |          |       |  |

|--------------------------------|-------------|-----------|----------|-------|--|

| Dimension                      | Limits      | MIN       | NOM      | MAX   |  |

| Number of Terminals            | N           |           | 24       |       |  |

| Pitch                          | е           |           | 0.50 BSC |       |  |

| Overall Height                 | Α           | 0.80      | 0.90     | 1.00  |  |

| Standoff                       | A1          | 0.00      | 0.02     | 0.05  |  |

| Terminal Thickness             | A3          | 0.203 REF |          |       |  |

| Overall Length                 | D           | 4.00 BSC  |          |       |  |

| Exposed Pad Length             | D2          | 2.40      | 2.50     | 2.60  |  |

| Overall Width                  | Е           | 4.00 BSC  |          |       |  |

| Exposed Pad Width              | E2          | 2.40      | 2.50     | 2.60  |  |

| Exposed Pad Index Chamfer      | CH          | 0.35 REF  |          |       |  |

| Terminal Width                 | b 0.20      |           |          | 0.30  |  |

| Terminal Length                | L           | 0.30      | 0.40     | 0.50  |  |

| Wettable Flank Step Cut Length | D3          | -         | -        | 0.085 |  |

| Wettable Flank Step Cut Height | A4          | 0.10      | -        | 0.19  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated

Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-21549 Rev A Sheet 2 of 2

DS20006369A-page 25 **Summary Datasheet** © 2020 Microchip Technology Inc.

# 24-Lead Very Thin Plastic Quad Flat, No Lead Package (UFB) - 4x4x1.0 mm Body [VQFN] With 2.50 mm Exposed Pad and Stepped Wettable Flanks

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### RECOMMENDED LAND PATTERN

|                                  | MILLIMETERS |      |          |      |

|----------------------------------|-------------|------|----------|------|

| Dimension                        | Limits      | MIN  | NOM      | MAX  |

| Contact Pitch                    | Е           |      | 0.50 BSC |      |

| Center Pad Width                 | X2          |      |          | 2.60 |

| Center Pad Length                | Y2          |      |          | 2.60 |

| Contact Pad Spacing              | C1          |      | 3.90     |      |

| Contact Pad Spacing              | C2          |      | 3.90     |      |

| Contact Pad Width (X24)          | X1          |      |          | 0.30 |

| Contact Pad Length (X24)         | Y1          |      |          | 0.85 |

| Contact Pad to Center Pad (X24)  | G1          | 0.23 |          |      |

| Contact Pad to Contact Pad (X20) | G2          | 0.20 |          |      |

| Thermal Via Diameter             | V           |      | 0.30     |      |

| Thermal Via Pitch EV             |             |      | 1.00     |      |

#### Notes:

- Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- 2. For best soldering results, thermal vias, if used, should be filled or tented to avoid solder loss during reflow process

Microchip Technology Drawing C04-23549 Rev A

# 9. Revision History

Revision A (Nov 2020)

Original release of the document.

# The Microchip Website

Microchip provides online support via our website at <a href="www.microchip.com">www.microchip.com</a>/. This website is used to make files and information easily available to customers. Some of the content available includes:

- **Product Support** Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQs), technical support requests, online discussion groups, Microchip design partner program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

## **Product Change Notification Service**

Microchip's product change notification service helps keep customers current on Microchip products. Subscribers will receive email notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, go to www.microchip.com/pcn and follow the registration instructions.

## **Customer Support**

Users of Microchip products can receive assistance through several channels:

- · Distributor or Representative

- · Local Sales Office

- Embedded Solutions Engineer (ESE)

- · Technical Support

Customers should contact their distributor, representative or ESE for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in this document.

Technical support is available through the website at: www.microchip.com/support

# **Product Identification System**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART<br>NO | I/O<br>Type | - | Temperature<br>Range | IC<br>Revision | Package<br>Option | Firmware<br>Revision | - | OTS | Shipping<br>Format | - | Product<br>Identifier |

|------------|-------------|---|----------------------|----------------|-------------------|----------------------|---|-----|--------------------|---|-----------------------|

| xxxxx      | У           | 1 | t                    | XXX            | ppp               | ff                   | - | СС  | S                  | 1 | VAO                   |

| Device:                    | TA100 |                                     |  |  |  |

|----------------------------|-------|-------------------------------------|--|--|--|

| I/O Type                   | Blank | SPI and I <sup>2</sup> C Interfaces |  |  |  |

|                            | Т     | I <sup>2</sup> C Interface Only     |  |  |  |

| Temperature Range:         | Υ     | -40°C to +125°C                     |  |  |  |

| IC Revision <sup>(2)</sup> | xxx   | Contact Microchip for Information   |  |  |  |

| Package Option             | C2X   | 8-Pin SOIC                          |  |  |  |

|                            | D3X   | 14-Pin SOIC                         |  |  |  |

|                            | UFB   | 24-Pad VQFN <sup>(3)</sup>          |  |  |  |

| Firmware Revision          | 01    | Firmware Release 01                 |  |  |  |

|                            | 02    | Firmware Release 02                 |  |  |  |

| OTS or Customer Code       | 00    | Standard Configuration              |  |  |  |

|                            | 10    | RSA (No ECC)                        |  |  |  |

|                            | 20    | Signed RSA (No ECC)                 |  |  |  |

|                            | 11    | RSA + ECC (Unsigned)                |  |  |  |

|                            | 01    | ECC (No RSA)                        |  |  |  |

|                            | 02    | Signed ECC (No RSA)                 |  |  |  |

|                            | 12    | Signed ECC (Unsigned RSA)           |  |  |  |

|                            | 21    | Signed RSA (Unsigned ECC)           |  |  |  |

|                            | 22    | Signed RSA + Signed ECC             |  |  |  |

| Shipping Options           | Т     | Tape and Reel <sup>(1)</sup>        |  |  |  |

|                            | В     | Bulk Units                          |  |  |  |

| Product Identifier         | VAO   | Generic Automotive Product          |  |  |  |

## Examples:

| Customer Ordering Code   | I/O<br>Interfaces     | Internal I <sup>2</sup> C<br>Pull-up | Package | Delivery      | Personalization        |

|--------------------------|-----------------------|--------------------------------------|---------|---------------|------------------------|

| TA100T-Y230C2X01-00T-VAO | I <sup>2</sup> C      | No                                   | SOIC-8  | Tape and Reel | Standard Configuration |

| TA100T-Y230C2X01-00B-VAO | I <sup>2</sup> C      | No                                   | SOIC-8  | Bulk          | Standard Configuration |

| TA100-Y230C2X01-00T-VAO  | SPI                   | _                                    | SOIC-8  | Tape and Reel | Standard Configuration |

| TA100-Y230C2X01-00B-VAO  | SPI                   | _                                    | SOIC-8  | Bulk          | Standard Configuration |

| TA100-Y230D3X01-00T-VAO  | I <sup>2</sup> C, SPI | No                                   | SOIC-14 | Tape and Reel | Standard Configuration |

| continued                              |                       |                                      |         |               |                        |

|----------------------------------------|-----------------------|--------------------------------------|---------|---------------|------------------------|

| Customer Ordering Code                 | I/O<br>Interfaces     | Internal I <sup>2</sup> C<br>Pull-up | Package | Delivery      | Personalization        |

| TA100-Y230D3X01-00B-VAO                | I <sup>2</sup> C, SPI | No                                   | SOIC-14 | Bulk          | Standard Configuration |

| TA100-V230UFB01-00T-VAO <sup>(3)</sup> | I <sup>2</sup> C, SPI | No                                   | VQFN-24 | Tape and Reel | Standard Configuration |

| TA100-V230UFB01-00B-VAO <sup>(3)</sup> | I <sup>2</sup> C, SPI | No                                   | VQFN-24 | Bulk          | Standard Configuration |

- Tape and Reel identifier only appears in the catalog part number description. This identifier is used for ordering purposes and is not printed on the device package. Check with your Microchip Sales Office for package availability with the Tape and Reel option.

- 2. IC Revision code indicates the base silicon revision and ROM code revision.

- 3. Contact Microchip Sales to determine the availability of the VQFN packaging option.

## **Microchip Devices Code Protection Feature**

Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is secure when used in the intended manner and under normal

conditions.

- There are dishonest and possibly illegal methods being used in attempts to breach the code protection features

of the Microchip devices. We believe that these methods require using the Microchip products in a manner

outside the operating specifications contained in Microchip's Data Sheets. Attempts to breach these code

protection features, most likely, cannot be accomplished without violating Microchip's intellectual property rights.

- Microchip is willing to work with any customer who is concerned about the integrity of its code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code

protection does not mean that we are guaranteeing the product is "unbreakable." Code protection is constantly

evolving. We at Microchip are committed to continuously improving the code protection features of our products.

Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act.

If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue

for relief under that Act.

# **Legal Notice**

Information contained in this publication is provided for the sole purpose of designing with and using Microchip products. Information regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDIRECT, SPECIAL, PUNITIVE, INCIDENTAL OR CONSEQUENTIAL LOSS, DAMAGE, COST OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

### **Trademarks**

The Microchip name and logo, the Microchip logo, Adaptec, AnyRate, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, chipKIT, chipKIT logo, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PackeTime, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AgileSwitch, APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, FlashTec, Hyper Speed Control, HyperLight Load, IntelliMOS, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, WinPath, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, Anyln, AnyOut, Augmented Switching, BlueSky, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, Espresso T1S, EtherGREEN, IdealBridge, In-Circuit Serial Programming, ICSP, INICnet, Intelligent Paralleling, Inter-Chip Connectivity, JitterBlocker, maxCrypto, maxView, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, RTAX, RTG4, SAM-ICE, Serial Quad I/O, simpleMAP, SimpliPHY, SmartBuffer, SMART-I.S., storClad, SQI, SuperSwitcher, SuperSwitcher II, Switchtec, SynchroPHY, Total Endurance, TSHARC, USBCheck, VariSense, VectorBlox, VeriPHY, ViewSpan, WiperLock, XpressConnect, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2020, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

ISBN: 978-1-5224-7021-2

# **Quality Management System**

For information regarding Microchip's Quality Management Systems, please visit www.microchip.com/quality.

# **Worldwide Sales and Service**

| AMERICAS                  | ASIA/PACIFIC          | ASIA/PACIFIC            | EUROPE                                      |

|---------------------------|-----------------------|-------------------------|---------------------------------------------|

| Corporate Office          | Australia - Sydney    | India - Bangalore       | Austria - Wels                              |

| 2355 West Chandler Blvd.  | Tel: 61-2-9868-6733   | Tel: 91-80-3090-4444    | Tel: 43-7242-2244-39                        |

| Chandler, AZ 85224-6199   | China - Beijing       | India - New Delhi       | Fax: 43-7242-2244-393                       |

| ГеІ: 480-792-7200         | Tel: 86-10-8569-7000  | Tel: 91-11-4160-8631    | Denmark - Copenhagen                        |

| Fax: 480-792-7277         | China - Chengdu       | India - Pune            | Tel: 45-4485-5910                           |

| Technical Support:        | Tel: 86-28-8665-5511  | Tel: 91-20-4121-0141    | Fax: 45-4485-2829                           |

| www.microchip.com/support | China - Chongqing     | Japan - Osaka           | Finland - Espoo                             |

| Web Address:              | Tel: 86-23-8980-9588  | Tel: 81-6-6152-7160     | Tel: 358-9-4520-820                         |

| www.microchip.com         | China - Dongguan      | Japan - Tokyo           | France - Paris                              |

| Atlanta                   | Tel: 86-769-8702-9880 | Tel: 81-3-6880- 3770    | Tel: 33-1-69-53-63-20                       |

| Ouluth, GA                | China - Guangzhou     | Korea - Daegu           | Fax: 33-1-69-30-90-79                       |

| el: 678-957-9614          | Tel: 86-20-8755-8029  | Tel: 82-53-744-4301     | Germany - Garching                          |

| ax: 678-957-1455          | China - Hangzhou      | Korea - Seoul           | Tel: 49-8931-9700                           |

| Austin, TX                | Tel: 86-571-8792-8115 | Tel: 82-2-554-7200      | Germany - Haan                              |

| Tel: 512-257-3370         | China - Hong Kong SAR | Malaysia - Kuala Lumpur | Tel: 49-2129-3766400                        |

| Boston                    | Tel: 852-2943-5100    | Tel: 60-3-7651-7906     | Germany - Heilbronn                         |

| Vestborough, MA           | China - Nanjing       | Malaysia - Penang       | Tel: 49-7131-72400                          |

| el: 774-760-0087          | Tel: 86-25-8473-2460  | Tel: 60-4-227-8870      | Germany - Karlsruhe                         |

| ax: 774-760-0088          | China - Qingdao       | Philippines - Manila    | Tel: 49-721-625370                          |

| Chicago                   | Tel: 86-532-8502-7355 | Tel: 63-2-634-9065      | Germany - Munich                            |

| tasca, IL                 | China - Shanghai      | Singapore               | Tel: 49-89-627-144-0                        |

| el: 630-285-0071          | Tel: 86-21-3326-8000  | Tel: 65-6334-8870       | Fax: 49-89-627-144-44                       |

| Fax: 630-285-0075         | China - Shenyang      | Taiwan - Hsin Chu       | Germany - Rosenheim                         |

| )allas                    | Tel: 86-24-2334-2829  | Tel: 886-3-577-8366     | Tel: 49-8031-354-560                        |

| Addison, TX               | China - Shenzhen      | Taiwan - Kaohsiung      | Israel - Ra'anana                           |

| el: 972-818-7423          | Tel: 86-755-8864-2200 | Tel: 886-7-213-7830     | Tel: 972-9-744-7705                         |

| Fax: 972-818-2924         | China - Suzhou        | Taiwan - Taipei         | Italy - Milan                               |

| Detroit                   | Tel: 86-186-6233-1526 | Tel: 886-2-2508-8600    | Tel: 39-0331-742611                         |

| lovi, MI                  | China - Wuhan         | Thailand - Bangkok      | Fax: 39-0331-466781                         |

| el: 248-848-4000          | Tel: 86-27-5980-5300  | Tel: 66-2-694-1351      | Italy - Padova                              |

| louston, TX               | China - Xian          | Vietnam - Ho Chi Minh   | Tel: 39-049-7625286                         |

| el: 281-894-5983          | Tel: 86-29-8833-7252  | Tel: 84-28-5448-2100    | Netherlands - Drunen                        |

| ndianapolis               | China - Xiamen        | 101. 04-20-0440-2100    | Tel: 31-416-690399                          |

| loblesville, IN           | Tel: 86-592-2388138   |                         | Fax: 31-416-690340                          |

| el: 317-773-8323          | China - Zhuhai        |                         | Norway - Trondheim                          |

| Fax: 317-773-5453         | Tel: 86-756-3210040   |                         | Tel: 47-72884388                            |

| el: 317-536-2380          | 161. 00-730-32100-40  |                         | Poland - Warsaw                             |

| os Angeles                |                       |                         | Tel: 48-22-3325737                          |

| Mission Viejo, CA         |                       |                         | Romania - Bucharest                         |

| el: 949-462-9523          |                       |                         | Tel: 40-21-407-87-50                        |

| Fax: 949-462-9608         |                       |                         | Spain - Madrid                              |

| el: 951-273-7800          |                       |                         | Tel: 34-91-708-08-90                        |

|                           |                       |                         | Fax: 34-91-708-08-91                        |

| Raleigh, NC               |                       |                         |                                             |

| el: 919-844-7510          |                       |                         | Sweden - Gothenberg<br>Tel: 46-31-704-60-40 |

| lew York, NY              |                       |                         |                                             |

| Tel: 631-435-6000         |                       |                         | Sweden - Stockholm                          |

| San Jose, CA              |                       |                         | Tel: 46-8-5090-4654                         |

| el: 408-735-9110          |                       |                         | UK - Wokingham                              |

| el: 408-436-4270          |                       |                         | Tel: 44-118-921-5800                        |

| Canada - Toronto          |                       |                         | Fax: 44-118-921-5820                        |

| Tel: 905-695-1980         |                       |                         |                                             |

| ax: 905-695-2078          |                       |                         |                                             |